K_FPGA基础

一、Technical Term(专业术语)

PLD: Programmable Logic Device可编程逻辑器件

DPLD: Complex Programmable Logic Device复杂可编程逻辑器件

FPGA: Field-Programmable Gate Array现场可编程门阵列

GAL:Generic Array Logic通用阵列逻辑

PLA:Programmable Logic Array可编程逻辑阵列

PAL:Programmable Array Logic可编程阵列逻辑

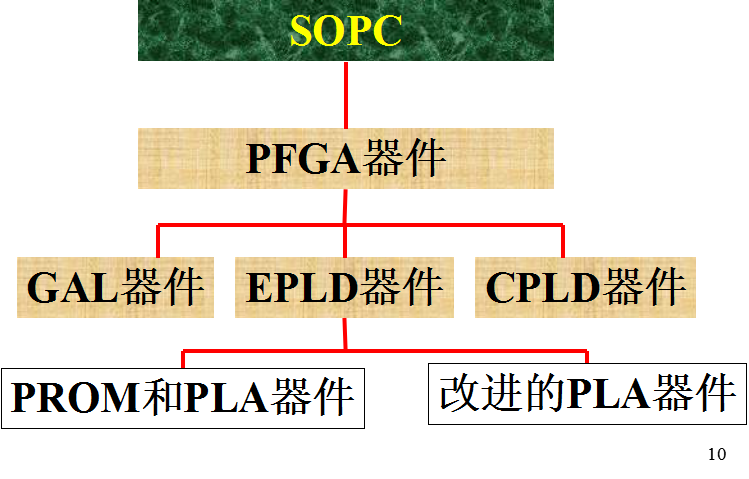

SOPC: System-on-a-Programmable-Chip可编程片上系统

LE:logic element逻辑单元

LUT:Lock up table查找表

SRAM:Static Random Access Memory静态随机存储器

EPROM:Erasable Programmable Read-Only Memory可擦写只读存储器

EEPROM:Electrically Erasable Programmable Read-Only Memory电可擦除只读存储器

ISP:in-system Programable 在系统编程

Altera、Xilinx、Lattice、Actel:主要的可编程逻辑器件生产厂家

PLD是20世纪70年代开始发展起来的一种新型大规模集成电路。其逻辑功能可由用户编程指定。PLD特别适宜于构造小批量生产的系统,或在系统开发研制过程中使用。

PAL特点:(1)采用“与”、“或”阵列对电路编程;

(2)一般采用熔丝工艺,一旦编程后便不能改写;

GAL器件采用高速电可擦CMOS工艺,能反复擦除和改写。 特别是在结构上采用了“输出逻辑宏单元”电路,使一种型号的GAL器件可以对几十种PAL器件做到全兼容, 给逻辑设计者带来了更大的灵活性。

FPGA是改变内部连接的布线来编程。

ISP:CPLD的设计是修改具有固定内部连接电路的逻辑功能来编程。

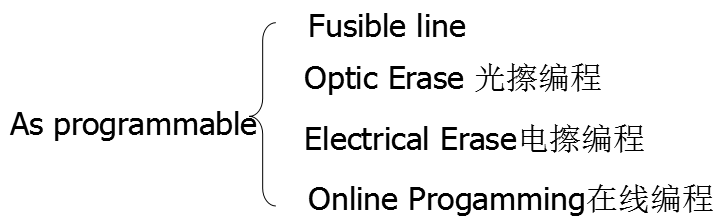

二、Development of PLD(PLD的发展)

三、PLD Type(PLD类型)

1.按集成度来划分,分为高密度和低密度PLD器件。

1)集成度小于1000 门/每片的LDPLD,又称简单PLD。

2)集成度大于1000门/每片的HDPLD

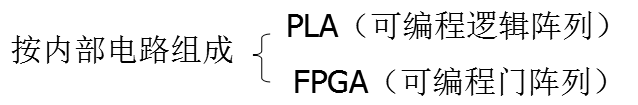

2.从结构上可分为:

1)乘积项结构器件:为“与—或”阵列结构,大部分简单PLD和CPLD都属于这个范畴;

2)查找表结构器件:由查找表组成可编程门,再构成阵列形式, FPGA属于此类器件。

3.从编程工艺上分为:

1)熔丝(Fuse)型器件:编程过程就是根据设计的熔丝图文件来烧断对应的熔丝,来达到编程的目的。编程后即使系统断电,它们中存 储的编程信息不会丢失 。

2)反熔丝(Antifuse)型器件:由Actel公司推出,在编程处通过击穿漏层使得两点之间获得导通。反熔丝PLD抗辐射,耐高低温,功耗低,速度快,在军品和宇航上有较大优势。

3)EPROM型:紫外线擦除电可编程逻辑器件,它用较高的编程电压进行编程,当需要再次编程时,用紫外线擦除。

4)EEPROM型:电可擦除可编程逻辑器件。CPLD采用此编程工艺

5)SRAM型:SRAM查找表结构的器件,大部分的FPGA采用此编程工艺。断电后编程信息会丢失,每次上电时,需从器件外部存储器将编程数据重新写入SRAM中。允许无限次编程。

6)Flash(Fastflash)型:即闪存技术,由Actel公司推出。采用此编程工艺的器件,可以实现多次可编程,也可以做到掉电后不需要重新配置。CPLD采用此编程工艺。

四、CPLD/FPGA 主要原理

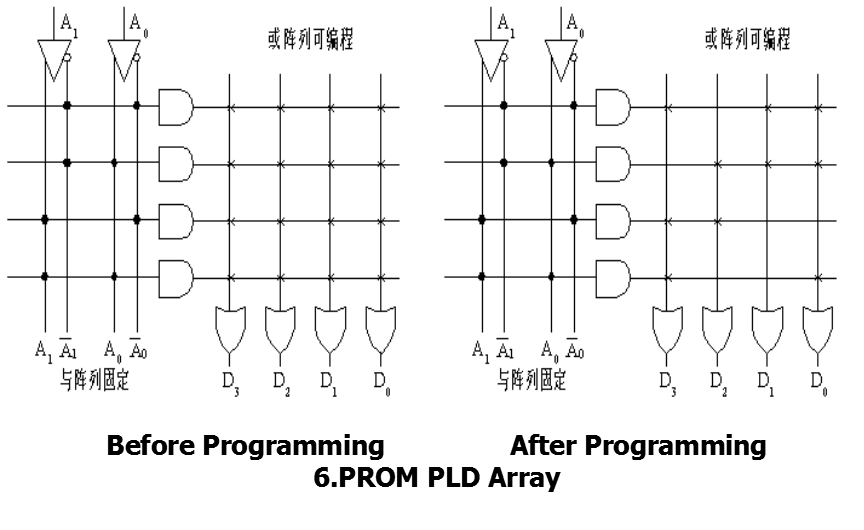

1. 任何组合函数都可以表示为与-或表达式:如 F=AB+BCD 。PLD由“与门阵列”和“或门阵列”加上输入输出电路构成。 早期的PLD有些是“与”阵列可编程,有些是“或”阵列可编程,还有些是“与”和“或”阵列都可编程。

2. 在可编程逻辑器件的基本结构中,由于与电路、或电路的数量很多,同时它们的排列又具有一定的规律性,因此常常将其称为与阵列及或阵列。

3. 基本结构中与阵列的输出称作乘积项。

4. 根据布尔代数原理,所有的逻辑函数都可以用与或表达式来表示,因此,由与或阵列构成的可编程逻辑器件可以很容易地实现数字系统的设计。

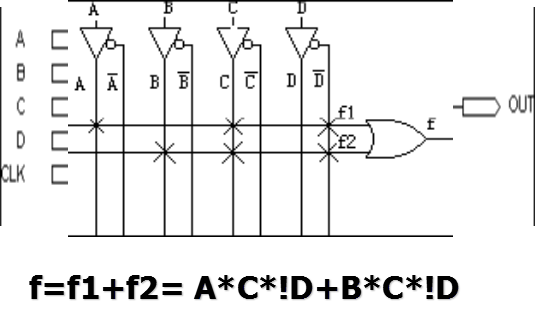

◆基于乘积项的PLD的基本结构及逻辑实现原理

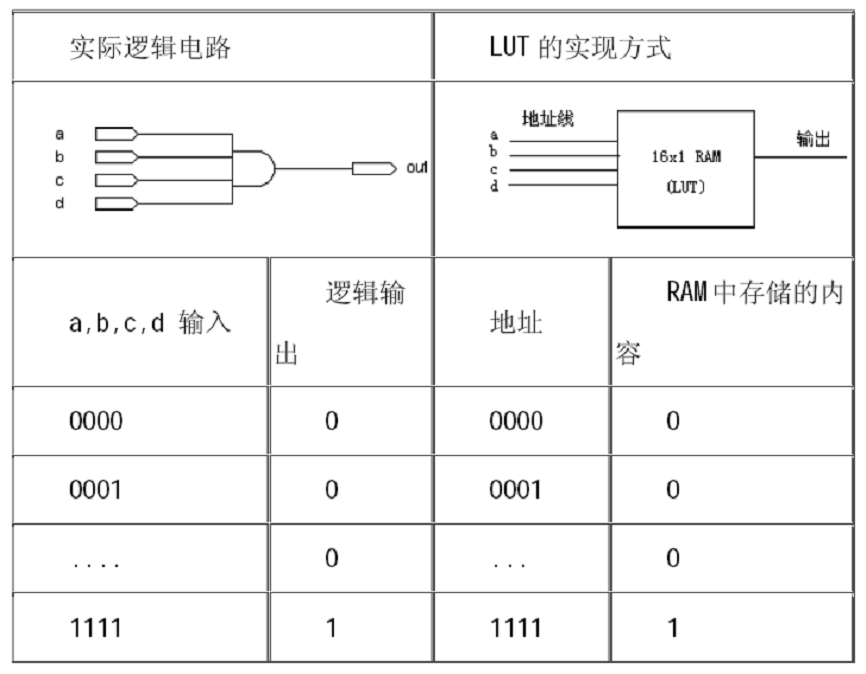

◆基于查找表的PLD的基本结构及逻辑实现原理

查找表LUT实质上是一个RAM,n位地址线可以配置为n×1的RAM。当用户描述了一个逻辑电路后,软件会计算所有可能的结果,并写入RAM。每一个信号进行逻辑运算,就等于输入一个地址进行查表,找出地址对应的内容,输出结果

五、FPGA/CPLD Construction(FPGA/CPLD结构)

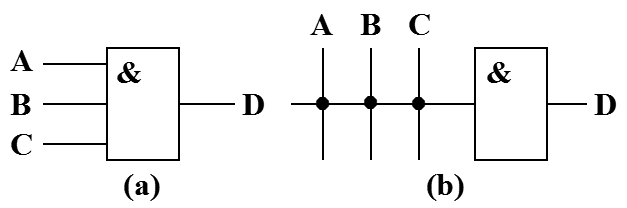

(一). 与门和或门

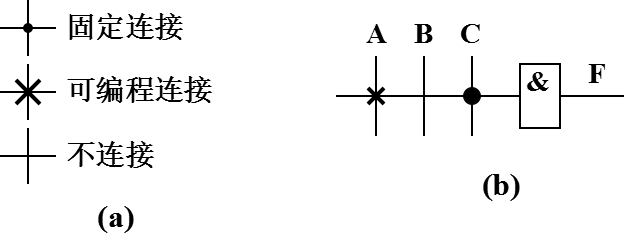

下图给出了3输入与门的两种表示法。传统表示法(图(a))中与门的3个输入A、B、C, 在PLD表示法(图(b))中称为3个输入项,而输出D称为“与”项。同样,或门也采用类似方法表示。

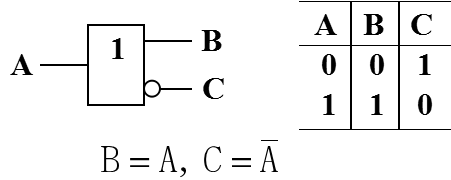

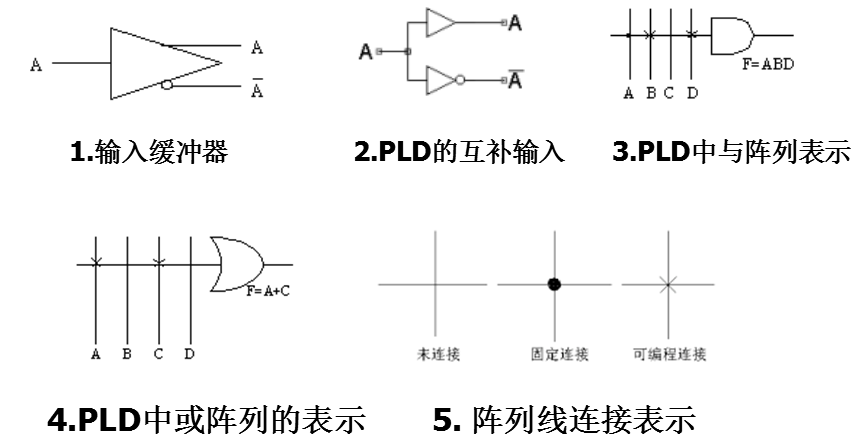

(二). 输入缓冲器

典型输入缓冲器的PLD表示法如右图所示。它的两个输出B、C是其输入A的原和反(见图中真值表)。

(三). 连接方式

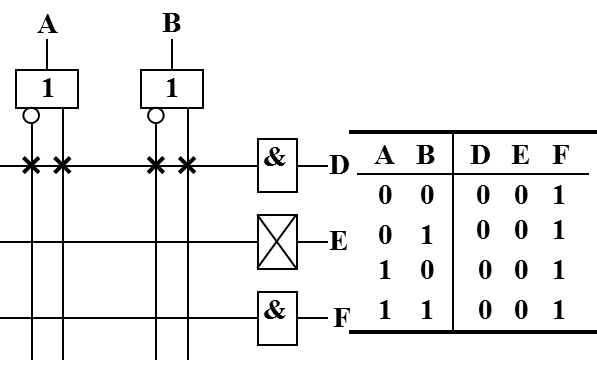

PLD阵列交叉点上的三种连接方式如图(a)所示。实点“·”表示硬线连接,即固定连接;“×”表示可编程连接;没有“×”和“·”的表示两线不连接。如图(b)中的输出F=A·C。

(四).与门不执行任何功能时的连接表示

用标有“×”标记的与门输出来表示所有输入缓冲器输出全部连到某一“与”项的情况,如图中输出E。

F表示无任何输入项与其相连,因此,该“与”项总是处于“浮动”的逻辑“1”。

D=A·!A·B·!B=0

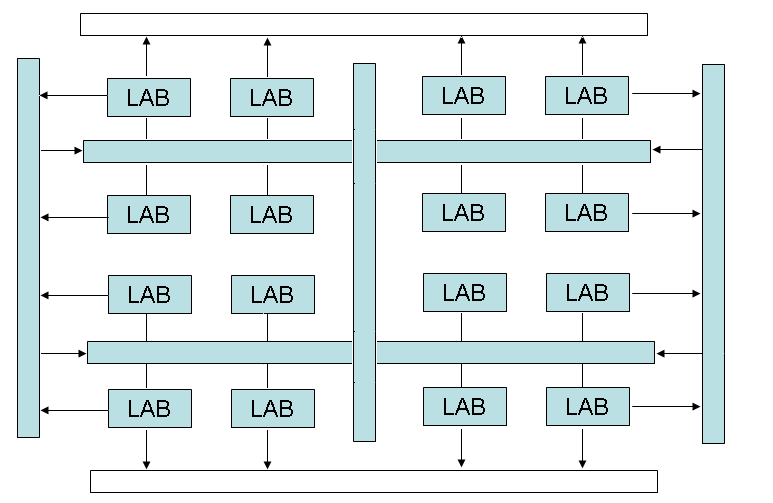

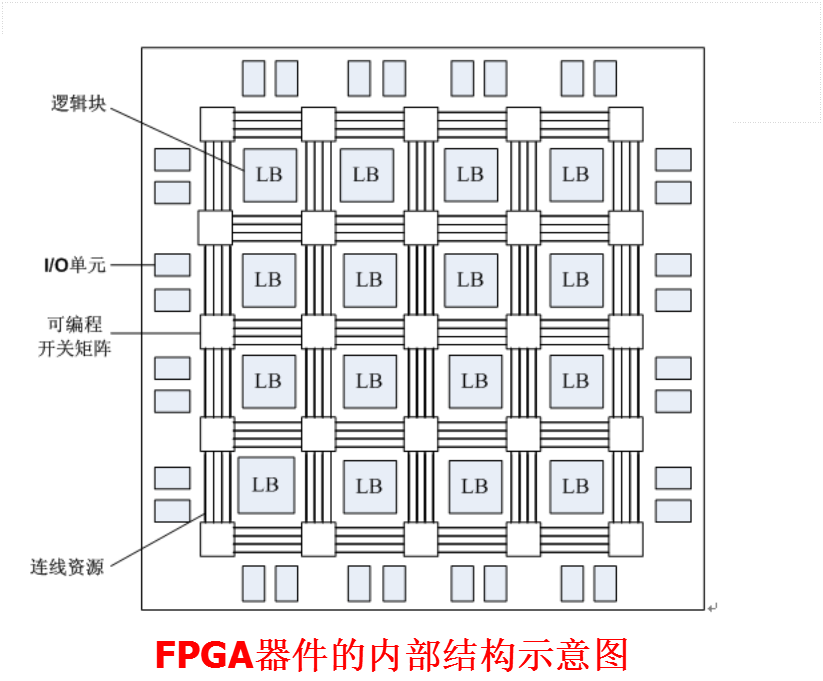

FPGA/CPLD的结构各有其特点和长处,但概括起来,它们是由三大部分组成的:

1.逻辑阵列块 LAB (Logic Array Block)或CLB(Configurable Logic Block),构成了PLD器件的逻辑组成核心。

2.输入/输出块 IOB(I/O Block)

3.连接逻辑块的可编程连线阵列 PIA (Programmable Interconnect Array)或互连资源 IR(Interconnect Resources).它由各种长度的连线线段组成,也有一些可编程的连接开关,用于逻辑块之间、逻辑块与输入/输出块之间的连接。

优点:

规模大,能够完成任何数字逻辑的功能,实现系统集成

在投片前验证设计的正确性,开发成本低

修改设计而不用改动硬件电路,开发周期短

减少PCB面积,提高系统可靠性

不同:

制造工艺不同

FPGA:查找表技术,SRAM工艺

CPLD:乘积项技术,Flash/EEPROM工艺

实现功能不同

FPGA:时序逻辑电路

CPLD:组合逻辑电路

六、FPGA设计方法

FPGA的常用设计方法包括“自顶向下”和“自下而上”,目前大规模FPGA设计一般选择“自顶向下”的设计方法。

七、FPGA/CPLD产品概述

Lattice公司CPLD器件系列

ispLSI器件的结构与特点

1. 采用UltraMOS工艺。

2. 系统可编程功能,所有的ispLSI器件均支持ISP功能。

3. 边界扫描测试功能。

4. 加密功能。

5. 短路保护功能。

ispMACH4000系列

ispMACH4000系列CPLD器件有3.3V、2.5V 和 1.8V 三种供电电压,分别属于 ispMACH 4000V、ispMACH 4000B 和 ispMACH 4000C 器件系列。

Lattice EC & ECP系列

Xilinx公司的FPGA和CPLD器件系列

1. Virtex-4系列FPGA

2. SpartanⅡ& Spartan-3 & Spartan 3E器件系列

3. XC9500 & XC9500XL系列CPLD

4. Xilinx FPGA配置器件SPROM

5. Xilinx的IP核

Altera公司FPGA和CPLD器件系列

1. Stratix II 系列FPGA

2. Stratix系列FPGA

3. ACEX系列FPGA

4. FLEX系列FPGA

5. MAX系列CPLD

6. Cyclone系列FPGA低成本FPGA

7. Cyclone II、III、IV、V、10等系列FPGA

8. MAX II、III、IV、V系列器件

9. Altera宏功能块及IP核

评论已关闭